# FS6128-04 PLL Clock Generator IC with VXCO

## 1.0 Key Features

- Phase-locked loop (PLL) device synthesizes output clock frequency from crystal oscillator or external reference clock

- On-chip tunable voltage-controlled crystal oscillator (VCXO) allows precise system frequency tuning

- Typically used for generation of MPEG-2 decoder clock

- 3.3V supply voltage

- · Very low phase noise PLL

- Use with "pullable" 14pF crystals no external padding capacitors required

- Small circuit board footprint (8-pin 0.150" SOIC)

- Custom frequency selections available contact your local ON Semiconductor sales representative for more information

## 2.0 Description

The FS6128 is a monolithic CMOS clock generator IC designed to minimize cost and component count in digital video/audio systems.

At the core of the FS6128 is circuitry that implements a voltage-controlled crystal oscillator (VCXO) when an external resonator (nominally 13.5MHz) is attached. The VCXO allows device frequencies to be precisely adjusted for use in systems that have frequency matching requirements, such as digital satellite receivers.

A high-resolution phase-locked loop generates an output clock (CLK) through a post-divider. The CLK frequency is ratiometrically derived from the VCXO frequency. The locking of the CLK frequency to other system reference frequencies can eliminate unpredictable artifacts in video systems and reduce electromagnetic interference (EMI) due to frequency harmonic stacking.

Table 1: Crystal / Output Frequencies

| Device   | f <sub>XIN</sub> (MHz) | CLK (MHz) |

|----------|------------------------|-----------|

| FS128-04 | 13.500                 | 27.000    |

Note: Contact ON Semiconductor for custom PLL frequencies.

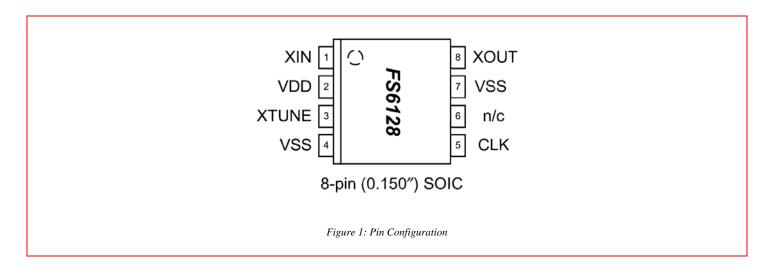

Table 2: Pin Descriptions

| Table 2.1 III Beech paets |      |       |                      |  |  |  |

|---------------------------|------|-------|----------------------|--|--|--|

| Pin                       | Type | Name  | Description          |  |  |  |

| 1                         | Al   | XIN   | VCXO feedback        |  |  |  |

| 2                         | Р    | VDD   | Power supply (+3.3V) |  |  |  |

| 3                         | Al   | XTUNE | VCXO tune            |  |  |  |

| 4                         | P    | VSS   | Ground               |  |  |  |

| 5                         | DO   | CLK   | Clock output         |  |  |  |

| 6                         | -    | n/c   | No connection        |  |  |  |

| 7                         | DO   | VSS   | Ground               |  |  |  |

| 8                         | AO   | XOUT  | VCXO drive           |  |  |  |

Key: AI = Analog Input; AO = Analog Output; DI = Digital Input; DI<sup>□</sup> = Input With Internal Pull-Up; DI<sub>□</sub> = Input With Internal Pull-Down; DIO = Digital Input/Output; DI-3 = Three-Level Digital Input, DO = Digital Output; P = Power/Ground; # = Active Low Pin

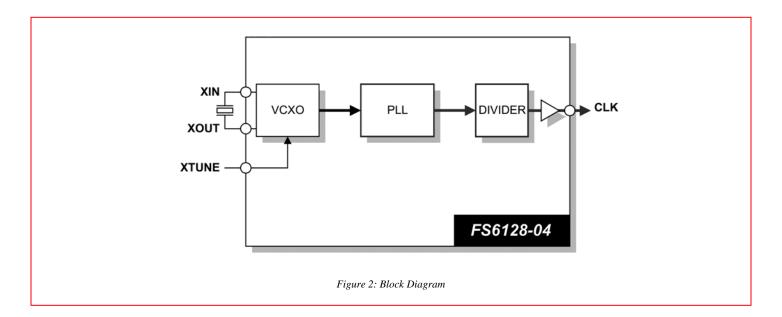

## 3.0 Functional Block Diagram

#### 3.1 Voltage-Controlled Crystal Oscillator (VCXO)

The VCXO provides a tunable, low-jitter frequency reference for the rest of the FS6128 system components. Loading capacitance for the crystal is internal to the FS6128. No external components (other than the resonator itself) are required for operation of the VCXO.

Continuous fine-tuning of the VCXO frequency is accomplished by varying the voltage on the XTUNE pin. The value of this voltage controls the effective capacitance presented to the crystal. The actual amount that this load capacitance change will alter the oscillator frequency depends on the characteristics of the crystal as well as the oscillator circuit itself.

It is important that the crystal load capacitance is specified correctly to "center" the tuning range. See Table 5.

A simple formula to obtain the "pulling" capability of a crystal oscillator is:

$$\Delta f(ppm) = \frac{C_1 \times (C_{L2} - C_{L1}) \times 10^6}{2 \times (C_0 + C_{L2}) \times (C_0 + C_{L1})}$$

where:

Co = the shunt (or holder) capacitance of the crystal

C1 = the motional capacitance of the crystal

CL1 and CL2 = the two extremes (minimum and maximum) of the applied load capacitance presented by the FS6128.

EXAMPLE: A crystal with the following parameters is used: C1 = 0.025pF and C0 = 6pF. Using the minimum and maximum CL1 = 10pF, and CL2 = 20pF, the tuning range (peak-to-peak) is:

$$\Delta f = \frac{0.025 \times (20 - 10) \times 10^6}{2 \times (6 + 20) \times (6 + 10)} = 300 \, ppm$$

#### 3.2 Phase-Locked Loop (PLL)

The on-chip PLL is a standard frequency- and phase locked loop architecture. The PLL multiplies the reference oscillator frequency to the desired output frequency by a ratio of integers. The frequency multiplication is exact with a zero synthesis error (unless otherwise specified).

## 4.0 Electrical Specifications

Table 3: Absolute Maximum Ratings

| Parameter                                                               | Symbol          | Min.           | Max.           | Units                    |

|-------------------------------------------------------------------------|-----------------|----------------|----------------|--------------------------|

| Supply voltage (V <sub>ss</sub> = ground)                               | $V_{DD}$        | $V_{SS} - 0.5$ | 7              | V                        |

| Input voltage, DC                                                       | VI              | $V_{SS} - 0.5$ | $V_{DD} + 0.5$ | V                        |

| Output voltage, DC                                                      | Vo              | $V_{SS} - 0.5$ | $V_{DD} + 0.5$ | V                        |

| Input clamp current, DC ( $V_1 < 0$ or $V_1 > V_{DD}$ )                 | I <sub>IK</sub> | -50            | 50             | mA                       |

| Output clamp current, DC ( $V_1 < 0$ or $V_1 > V_{DD}$ )                | lok             | -50            | 50             | mA                       |

| Storage temperature range (non-condensing)                              | Ts              | -65            | 150            | °C                       |

| Ambient temperature range, under bias                                   | T <sub>A</sub>  | -55            | 125            | °C                       |

| Junction temperature                                                    | TJ              |                | 125            | °C                       |

| Re-flow solder profile                                                  |                 |                |                | Per IPC/JEDEC J-STD-020B |

| Input static discharge voltage protection (MLD-STD 883E, Method 3015.7) |                 |                | 2              | kv                       |

Note: Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These conditions represent a stress rating only and functional operation of the device at these or any other conditions above the operational limits noted in this specification is not implied. Exposure to maximum rating conditions for extended conditions may affect device performance, functionality and reliability.

#### CAUTION: ELECTROSTATIC SENSITIVE DEVICE

Permanent damage resulting in a loss of functionality or performance may occur if this device is subjected to a high energy electrostatic discharge.

Table 4: Operating Conditions

| Parameter                           | Symbol            | Conditions/Descriptions | Min. | Тур. | Max. | Units |

|-------------------------------------|-------------------|-------------------------|------|------|------|-------|

| Supply voltage                      | $V_{DD}$          | 3.3V ± 10%              | 3.0  | 3.3  | 3.6  | V     |

| Ambient operating temperature range | T <sub>A</sub>    | 0                       |      |      | 70   | °C    |

| Crystal resonator frequency         | f <sub>XTAL</sub> | Functional mode         | 12   | 13.5 | 18   | MHz   |

Table 5: DC Electrical Specifications

| Parameter                                            | Symbol                             | Conditions/Descriptions                                                          | Min.      | Тур.     | Max. | Units |

|------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------|-----------|----------|------|-------|

| Overall                                              | -                                  |                                                                                  |           |          |      |       |

| Supply current, dynamic, with loaded outputs         | I <sub>DD</sub>                    | f <sub>XAL</sub> = 13.5MHz; CL = 10pF; VDD = 3.6V                                |           | 30       |      | mA    |

| Supply current, static                               | I <sub>DD</sub>                    | XIN = 0V; VDD = 3.6V                                                             |           | 3        |      | mA    |

| Voltage-Controlled Crystal Oscillator (conta         | act factory fo                     | r approved crystal sources or other application                                  | ation ass | istance) |      |       |

| Crystal loading capacitance at center tuning voltage | $C_{L(xtal)}$                      | Order crystal for this capacitance (parallel load) at desired center frequency   |           | 14       |      | pF    |

| Crystal resonator motional capacitance               | C <sub>1</sub>                     | Specified motional capacitance of the crystal will affect pullability (see text) |           | 25       |      | fF    |

| XTUNE effective range                                |                                    |                                                                                  | 0         |          | 3    | V     |

| Synthesized load capacitance min.                    | C <sub>L1</sub>                    | @V(XTUNE) = minimum value                                                        |           | 10       |      | pF    |

| Synthesized load capacitance max.                    | C <sub>L2</sub>                    | @V(XTUNE) = maximum value                                                        |           | 20       |      | pF    |

| VCXO tuning range                                    |                                    | $f_{XTAL}$ = 13.5MHz; $C_{L(xtal)}$ = 14pF; $C_{1}(xtal)$ = 25fF (peak-to-peak)  |           | 300      |      | ppm   |

| VCXO tuning characteristic                           |                                    | Note: positive change of XTUNE = positive change of VCXO frequency               |           | 150      |      | ppm/V |

| Crystal drive level                                  |                                    | $R_{XTAL} = 20\Omega$ ; $C_L = 20pF$                                             |           | 200      |      | μW    |

| Clock Output (CLK)                                   |                                    |                                                                                  |           |          |      |       |

| High-level output source current*                    | I <sub>OH</sub>                    | V <sub>O</sub> = 2.0V                                                            |           | -40      |      | mA    |

| Low-level output sink current*                       | I <sub>OL</sub>                    | $V_0 = 0.4V$                                                                     |           | 17       |      | mA    |

| Output impedance*                                    | Z <sub>OH</sub><br>Z <sub>OL</sub> | $V_O = 0.1V_{DD}$ ; output driving high $V_O = 0.1V_{DD}$ ; output driving low   |           | 25<br>25 |      | Ω     |

| Short circuit source current*                        | I <sub>OSH</sub>                   | $V_O = 0V$ ; shorted for 30s, max.                                               |           | -55      |      | mA    |

| Short circuit sink current*                          | I <sub>OSL</sub>                   | $V_0$ = 3.3V; shorted for 30s, max.                                              |           | 55       |      | mA    |

Note: Unless otherwise stated  $V_{DD}$  = 3.3V ±10% no load on any output and ambient temperature range  $T_A$  = 0°C to 70°C. Parameters denoted with an asterisk (\*) represent nominal characterization data and are not production tested to any specific limits. Where given, MIN and MAX characterization data are ±3 $\sigma$  from typical. Negative currents indicate current flows out of the device.

Table 6: AC Timing Specifications

| Parameter                                     | Symbol Conditions/Descriptions |                                                                                                                         | Min. | Тур. | Max. | Units |  |  |

|-----------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--|--|

| Overall                                       |                                |                                                                                                                         |      |      |      |       |  |  |

| VCXO stabilization time* t <sub>VCXOSTB</sub> |                                | From power valid                                                                                                        |      | 10   |      | ms    |  |  |

| PLL stabilization time*                       | t <sub>PLLSTB</sub>            | From VCXO stable                                                                                                        |      | 100  |      | μs    |  |  |

| Synthesis error                               |                                | (Unless otherwise noted in frequency table)                                                                             |      | 0    |      | ppm   |  |  |

| Clock Output (CLK)                            |                                |                                                                                                                         |      |      |      |       |  |  |

| Duty cycle*                                   |                                | Ratio of high pulse width (as measured from rising edge to next falling edge at V <sub>DD</sub> /2) to one clock period | 45   |      | 55   | %     |  |  |

| Jitter, period (peak-peak)*                   | t <sub>i(ΔP)</sub>             | From rising edge to next rising edge at $V_{DD}/2$ , CL = 10pF 200 ps                                                   |      | 200  |      | ps    |  |  |

| Jitter, long term ( $σ$ γ( $τ$ )              | t <sub>j(LT)</sub>             | From 0-500µs at V <sub>DD</sub> /2, CL = 10pF compared to ideal clock source                                            |      | 100  |      | ps    |  |  |

| Rise time* t <sub>r</sub>                     |                                | $V_{DD} = 3.3V$ ; $V_{O} = 0.3V$ to 3.0V; $C_{L} = 10pF$                                                                |      | 1.7  |      | ns    |  |  |

| Fall time*                                    | t <sub>f</sub>                 | $V_{DD} = 3.3V$ ; $V_{O} = 3.0V$ to $0.3V$ ; $C_{L} = 10pF$                                                             |      | 1.7  |      | ns    |  |  |

Note: Unless otherwise stated,  $V_{DD}$  = 3.3V ±10%, no load on any output, and ambient temperature range  $T_A$  = 0°C to 70°C. Parameters denoted with an asterisk (\*) represent nominal characterization data and are not production tested to any specific limits. Where given, MIN and MAX characterization data are ±3 $\sigma$  from typical.

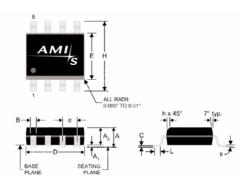

# 5.0 Package Information – For Both 'Green' and 'Non-Green'

Table 7: 8-pin SOIC (0.150") Package Dimensions

|    | Dimensions |        |       |        |  |  |

|----|------------|--------|-------|--------|--|--|

|    | Inc        | hes    | Milli | meters |  |  |

|    | Min.       | Max.   | Min.  | Max.   |  |  |

| Α  | 0.061      | 0.068  | 1.55  | 1.73   |  |  |

| A1 | 0.004      | 0.0098 | 0.102 | 0.249  |  |  |

| A2 | 0.055      | 0.061  | 1.40  | 1.55   |  |  |

| В  | 0.013      | 0.019  | .033  | 0.49   |  |  |

| С  | 0.0075     | 0.0098 | 0.191 | 0.249  |  |  |

| D  | 0.189      | 0.196  | 4.80  | 4.98   |  |  |

| Ε  | 0.150      | 0.157  | 3.81  | 3.99   |  |  |

| е  | 0.05       | O BSC  | 1.2   | 7 BSC  |  |  |

| Н  | 0.230      | 0.244  | 5.84  | 6.20   |  |  |

| h  | 0.010      | 0.016  | 0.25  | 0.41   |  |  |

| L  | 0.016      | 0.035  | 0.41  | 0.89   |  |  |

| Θ  | 0°         | 8°     | 0°    | 8°     |  |  |

Table 8: 8-pin SOIC (0.150") Package Characteristics

| Parameter                                                 | Symbol          | Conditions/Descriptions       | Тур. | Units |

|-----------------------------------------------------------|-----------------|-------------------------------|------|-------|

| Thermal impedance, junction to free-air 8-pin 0.150" SOIC | $\Theta_{JA}$   | Air flow = 0 m/s              | 110  | °C/W  |

| Lead inductance, self                                     | L <sub>11</sub> | Corner lead                   | 2.0  | nΗ    |

| Load industance mutual                                    | L <sub>12</sub> | Center lead                   | 1.6  | nH    |

| Lead inductance, mutual                                   |                 | Any lead to any adjacent lead | 0.4  | ПП    |

| Lead capacitance, bulk                                    | C <sub>11</sub> | Andy lead to V <sub>SS</sub>  | 0.27 | pF    |

## **6.0 Ordering Information**

| Part Number    | Package                                            | Shipping Configuration | Temperature Range        |

|----------------|----------------------------------------------------|------------------------|--------------------------|

| FS6128-04G-XTD | 8-pin (0.150") SOIC                                | Tube/Tray              | 0°C to 70°C (commercial) |

|                | 'Green' or lead-free packaging                     |                        |                          |

| FS6128-04G-XTP | 8-pin (0.150") SOIC 'Green' or lead-free packaging | Tape & Reel            | 0°C to 70°C (commercial) |

## 7.0 Revision History

| Revision | Date       | Modification                            |

|----------|------------|-----------------------------------------|

| 1        | March 2004 | Initial release                         |

| 2        | May 2008   | Update to new ON Semiconductor template |

|          |            |                                         |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA **Phone:** 303-675-2175 or 800-344-3860 Toll Free USA/Canada **Fax:** 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

**Japan Customer Focus Center** Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local

Sales Representative